格式:pdf

大小:358KB

頁數: 3頁

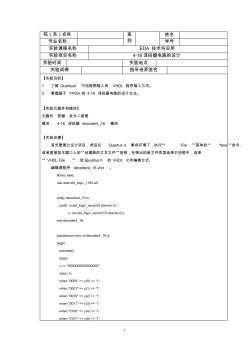

1 院(系)名稱 班 別 姓名 專業名稱 學號 實驗課程名稱 EDA 技術與應用 實驗項目名稱 4-16譯碼器電路的設計 實驗時間 實驗地點 實驗成績 指導老師簽名 【實驗目的】 1. 了解 QuartusII 中電路圖輸入和 VHDL 程序輸入方式。 2. 掌握基于 FPGA 的 4-16 譯碼器電路的設計方法。 【實驗元器件和模塊】 元器件:按鍵、發光二極管 模塊: 4-16 譯碼器 decoder4_16 模塊 【實驗步驟】 首先要建立設計項目,然后在 Quartus II 集成環境下,執行“ File ”菜單的“ New”命令, 或者直接按主窗口上的“創建新的文本文件”按鈕,在彈出的新文件類型選擇對話框中,選擇 “ VHDL File ”,進入Quartus II 的 VHDL 文本編輯方式。 編輯源程序 decoder4_16.vhd 。 library ieee; use

格式:pdf

大小:95KB

頁數: 3頁

【例 4.15】用模塊例化方式設計 8位計數譯碼器電路系統。 在 8 位計數譯碼系統電路設計中, 需要事先設計一個 4 位二進制加法計數器 cnt4e 模塊 和一個七段數碼顯示器的譯碼器 dec7s模塊,然后用模塊例化方式將這兩種模塊組成計數譯 碼系統電路。 1. 4位二進制加法計數器 cnt4e 的設計 cnt4e 的元件符號如圖 4.11 所示, clk 是時鐘輸入端; clr 是復位控制輸入端,當 clr=1 時計數器被復位,輸出 q[3..0]=0000;ena 是使能控制輸入端,當 ena=1 時,計數器才能工 作; cout 是進位輸出端,當輸出 q[3..0]=1111 時, cout=1。 Cnt4e 的 Verilog HDL 源程序 cnt4e.v 如下: module cnt4e (clk,clr,ena,cout,q); input clk,clr,ena; o

熱門知識

138譯碼器精華知識

138譯碼器-

話題: 建筑設計songkaisong

最新知識

138譯碼器-

話題: 地產家居CHINAEPTECH

-

話題: 工程造價45dj2679li

相關問答

138譯碼器- 寬6.6米長13米房子設計圖

- 瀝青標號AC-13C是什么意思

- 住宅多少層噪聲最大13層

- 裝修省錢13個秘訣

- 借土回填套13清單哪項

- 泳池底板怎么套定額13廣東

- 云南安裝13定額

- 國家建筑標準設計圖集13j14

- 河北省13清單問題

- 湖北13清單定額

- 桂電財〔2009〕138號(費舊物資處理管理辦法)

- JGJ138-2001型鋼混凝土組合結構技術規程

- K172+138~K171+230排水溝開工報告

- 建質[2017]138號質量保證金管理辦法

- 主跨138米預應力砼連續梁橋的施工控制

- 138石材幕墻工程檢驗批質量驗收記錄

- 138m高雙薄壁空心橋墩翻模施工技術

- TR138D型旋挖鉆機

- 南車TR138D型旋挖鉆機

- EDA4-16譯碼器電路設計

- 歐洲標準目錄系列無損檢測TC138

- 基于壓電堆驅動器的噴嘴擋板式氣體控制閥

- 電氣工程及其自動化特色專業建設探索

- 分形DGS單元結構設計及其在微帶電路中的應用

- 磷銨技術改造五大磷肥工程的建議

- 以大豆油多元醇制備的硬質聚氨酯泡沫塑料的性能

- 逆變TIG焊機接觸引弧電路的設計(引弧電路)

- 138譯碼器真值表

- 138酸性玻璃膠

- 1390噴頭

- 1394是什么

- 1394網絡適配器

- 1394連接是什么

- 139平米裝修效果圖

- 13A250V三極帶開關帶燈方腳插座

- 13A250V三極帶開關方腳插座

- 13A250V三極方腳插座

- 13A250V單聯帶開關帶熔絲管接線座

- 13A250V單聯帶熔絲管接線座

- 13A250V雙聯三極帶開關方腳插座

- 13A250V雙聯三極方腳插座

- 13A250V雙聯帶開關帶燈帶熔絲管接線座

- 13A250V雙聯帶開關帶熔絲管接線座

- 13A250V帶開關方腳插座

- 13A250V帶熔絲管三極方腳插座

- 13A250V方腳插座

- 13Abs雙聯插座

- 13Abs帶開關雙聯插座

- 13Abs帶開關插座

- 13A萬能插

- 13A萬能插座功能模塊

- 13A三方插

- 13A三方插座

- 13A三極方插座

- 13A三極方腳插座

- 13A保險連接器

- 13A雙路開關萬能插座