格式:pdf

大小:358KB

頁數: 3頁

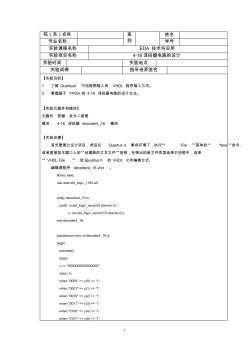

1 院(系)名稱 班 別 姓名 專業名稱 學號 實驗課程名稱 EDA 技術與應用 實驗項目名稱 4-16譯碼器電路的設計 實驗時間 實驗地點 實驗成績 指導老師簽名 【實驗目的】 1. 了解 QuartusII 中電路圖輸入和 VHDL 程序輸入方式。 2. 掌握基于 FPGA 的 4-16 譯碼器電路的設計方法。 【實驗元器件和模塊】 元器件:按鍵、發光二極管 模塊: 4-16 譯碼器 decoder4_16 模塊 【實驗步驟】 首先要建立設計項目,然后在 Quartus II 集成環境下,執行“ File ”菜單的“ New”命令, 或者直接按主窗口上的“創建新的文本文件”按鈕,在彈出的新文件類型選擇對話框中,選擇 “ VHDL File ”,進入Quartus II 的 VHDL 文本編輯方式。 編輯源程序 decoder4_16.vhd 。 library ieee; use

格式:pdf

大小:95KB

頁數: 3頁

【例 4.15】用模塊例化方式設計 8位計數譯碼器電路系統。 在 8 位計數譯碼系統電路設計中, 需要事先設計一個 4 位二進制加法計數器 cnt4e 模塊 和一個七段數碼顯示器的譯碼器 dec7s模塊,然后用模塊例化方式將這兩種模塊組成計數譯 碼系統電路。 1. 4位二進制加法計數器 cnt4e 的設計 cnt4e 的元件符號如圖 4.11 所示, clk 是時鐘輸入端; clr 是復位控制輸入端,當 clr=1 時計數器被復位,輸出 q[3..0]=0000;ena 是使能控制輸入端,當 ena=1 時,計數器才能工 作; cout 是進位輸出端,當輸出 q[3..0]=1111 時, cout=1。 Cnt4e 的 Verilog HDL 源程序 cnt4e.v 如下: module cnt4e (clk,clr,ena,cout,q); input clk,clr,ena; o

- 科勒衛浴合川專賣店地址

- 總線地址模塊套什么定額

- 一建視頻下載地址

- 玉蘭墻紙官網地址是多少

- 華藝衛浴陶瓷潔具工廠地址

- 蕪湖信義玻璃廠地址

- 西安東鵬瓷磚地址

- 鋼構cad下載地址

- 天津市房管局地址

- 陜西二建一公司地址

- 基于壓電堆驅動器的噴嘴擋板式氣體控制閥

- 磷銨技術改造五大磷肥工程的建議

- 以大豆油多元醇制備的硬質聚氨酯泡沫塑料的性能

- 逆變TIG焊機接觸引弧電路的設計(引弧電路)

- 應用模糊數學理論對公路工程建設項目方案的綜合評價

- 可替代現有隔熱保溫材料的新型材料

- 以貫穿項目為核心載體的建筑工程技術專業素材庫建設

- 多逆變器太陽能光伏并網發電系統的組群控制方法

- 影響萘高效減水劑與普通硅酸鹽水泥適應性的關鍵因素

- 在全縣非煤礦山和危化企業安全生產工作會議上的講話

- 中國工程造價咨詢業的發展趨勢

- 支持并行工程和智能CAPP的制造資源建模技術

- 中共重慶市委重慶市人民政府關于建設平安重慶的決定

- 智能建筑工程報警與電視監控系統前端設備的安裝施工

- 在“建筑節能與居住舒適”專題技術交流會議上的講話

- 以MSP430FW427為核心的遠程數字水表設計

- 園林綠化養護精細化管理對河源市園林景觀的影響分析