格式:pdf

大小:358KB

頁數: 3頁

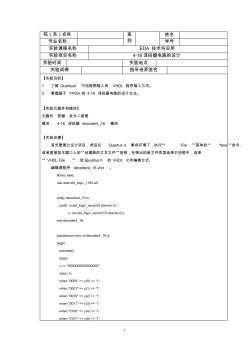

1 院(系)名稱 班 別 姓名 專業名稱 學號 實驗課程名稱 EDA 技術與應用 實驗項目名稱 4-16譯碼器電路的設計 實驗時間 實驗地點 實驗成績 指導老師簽名 【實驗目的】 1. 了解 QuartusII 中電路圖輸入和 VHDL 程序輸入方式。 2. 掌握基于 FPGA 的 4-16 譯碼器電路的設計方法。 【實驗元器件和模塊】 元器件:按鍵、發光二極管 模塊: 4-16 譯碼器 decoder4_16 模塊 【實驗步驟】 首先要建立設計項目,然后在 Quartus II 集成環境下,執行“ File ”菜單的“ New”命令, 或者直接按主窗口上的“創建新的文本文件”按鈕,在彈出的新文件類型選擇對話框中,選擇 “ VHDL File ”,進入Quartus II 的 VHDL 文本編輯方式。 編輯源程序 decoder4_16.vhd 。 library ieee; use

格式:pdf

大小:95KB

頁數: 3頁

【例 4.15】用模塊例化方式設計 8位計數譯碼器電路系統。 在 8 位計數譯碼系統電路設計中, 需要事先設計一個 4 位二進制加法計數器 cnt4e 模塊 和一個七段數碼顯示器的譯碼器 dec7s模塊,然后用模塊例化方式將這兩種模塊組成計數譯 碼系統電路。 1. 4位二進制加法計數器 cnt4e 的設計 cnt4e 的元件符號如圖 4.11 所示, clk 是時鐘輸入端; clr 是復位控制輸入端,當 clr=1 時計數器被復位,輸出 q[3..0]=0000;ena 是使能控制輸入端,當 ena=1 時,計數器才能工 作; cout 是進位輸出端,當輸出 q[3..0]=1111 時, cout=1。 Cnt4e 的 Verilog HDL 源程序 cnt4e.v 如下: module cnt4e (clk,clr,ena,cout,q); input clk,clr,ena; o

- 12YJ8第74頁的室外鋼梯

- 12YJ8第74頁的鋼梯計算過程

- 12YJ8第74頁的鋼梯重量

- 12YJ8第74頁鋼梯的計算

- 非公開招標74號令

- 財政部非公開招標74號

- 公開招標74號

- 招標采購74號文

- 政府非招標采購74

- 政府采購非招標74號

- Macha譯碼器的技術改造及檢修程序的開發

- EDA4-16譯碼器電路設計

- 基于壓電堆驅動器的噴嘴擋板式氣體控制閥

- 電氣工程及其自動化特色專業建設探索

- 分形DGS單元結構設計及其在微帶電路中的應用

- 磷銨技術改造五大磷肥工程的建議

- 以大豆油多元醇制備的硬質聚氨酯泡沫塑料的性能

- 逆變TIG焊機接觸引弧電路的設計(引弧電路)

- 預制砌塊(磚、石)擋土墻工程砌體施工安全技術交底

- 應用模糊數學理論對公路工程建設項目方案的綜合評價

- 引嫩工程擴建區土壤水鹽動態與防治土壤鹽堿措施

- 中華華丹雨、污水管道溝槽開挖專項施工方案教學教材

- 中國工程圖學學會成立工程與制造系統集成化分會

- 中國吹制玻璃行業市場前景分析預測年度報告(目錄)

- 可替代現有隔熱保溫材料的新型材料

- 醫院病房樓工程施工裝飾裝修工程施工控制

- 在生活中構筑自然——河南天旺園林工程有限公司剪影

- 74138譯碼器真值表

- 7413環氧聚酰胺底漆

- 74161計數器功能

- 74161計數器功能表

- 741xj消防信號蝶閥

- 741X雙腔隔膜式可調減壓閥

- 741X過濾活塞式水位控制閥

- 741X過濾活塞式流量控制閥

- 741X過濾活塞式電動控制閥

- 741式卡頭

- 742X雙腔式安全泄壓閥

- 742電磁閥

- 743X多功能水泵控制閥

- 745X雙腔隔膜式浮球閥

- 745X過濾活塞式電動浮球閥

- 745X過濾活塞式遙控浮球閥

- 745X遙控浮球閥

- 745系列推拉窗

- 746X可調減壓穩壓閥

- 7470d粉盒

- 7475超硬鋁板

- 74hc138譯碼器

- 74kw履帶推土機圖片

- 74ls138譯碼器

- 74ls161計數器功能

- 74平兩室一廳裝修圖

- 74平兩室一廳裝修效果圖

- 74平小戶型裝修實例

- 74平方小戶型裝修

- 74平米三室一廳裝修圖