基于數據選擇器和D觸發器的多輸入時序電路設計

格式:pdf

大小:680KB

頁數:3P

人氣 :90

4.6

為了探索多輸入時序邏輯電路的簡便實現方法,介紹了基于數據選擇器和D觸發器的多輸入時序邏輯電路設計技術。即將D觸發器和數據選擇器進行組合,用觸發器的現態作為數據選擇器選擇輸入變量、數據選擇器的輸出函數作為觸發器的D輸入信號,構成既有存儲功能又有數據選擇功能的多輸入端時序網絡。由觸發器的現態選擇輸入變量、所選擇的輸入變量決定觸發器的次態轉換方向。該方法適合實現互斥多變量時序邏輯電路,且在設計過程中不需要進行函數化簡。

一種基于D觸發器的調制編碼板故障記憶電路設計

格式:pdf

大小:154KB

頁數:2P

對于廣播發射機的日常維護工作,準確的判斷發射機的故障點是快速處理發射機故障的先決條件。在dx-200型中波發射機中,一些故障由于故障指示瞬間消失或者故障指示不能覆蓋到給維護人員判斷故障位置、縮短處理故障的時間帶來了負擔。以調制編碼板的電源故障指示電路為載體,本文用d觸發器設計出一種穩定可靠的故障點記憶電路,在實際運行中把故障現場保持記憶,留給維護人員,大大提高了故障處理效率。

編輯推薦下載

一種抗單粒子全加固D觸發器的設計

格式:pdf

大小:1.1MB

頁數:5P

4.7

采用當前成熟的兩種抗單粒子翻轉鎖存器構成了主從d觸發器,在d觸發器加固設計中引入了時鐘加固技術,對輸出也采用了加固設計。仿真對比顯示本設計的加固效果優于國內同類設計。

基于D觸發器的2N進制循環碼產生器的設計

格式:pdf

大小:589KB

頁數:1P

4.5

用傳統時序邏輯電路設計方法,可實現利用d觸發器對2n進制循環碼產生電路的設計。但設計過程較繁瑣,容易出錯。針對上述問題提出了一種利用d觸發器設計2n進制循環碼產生電路的簡單方法。

數據選擇器和D觸發器的多輸入時序電路設計熱門文檔

門電路和觸發器

格式:pdf

大小:2.0MB

頁數:8P

4.6

1 第九節門電路和觸發器 電子電路通常分模擬電子電路和數字電子電路兩大類。前面介紹的放大電路屬于第 一類,電路中的工作信號是連續變化的電信號(模擬信號)。數字電路的基本工作信號是 二進制的數字信號,它在時間上和數值上是離散的,即不是連續漸變的,而且只有0和 1兩個基本數字,反映在電路上就是低電平和高電平兩種狀態。因此在穩態時,電路中 的半導體器件都是工作在開、關狀態。數字電路是由幾種最基本的單元電路組成的。在 這些基本單元中,對元件的精度要求不高,只要在工作時能夠可靠地區分0和1兩種狀 態就可以了。數字電路中研究的主要問題是輸入信號的狀態(0或1)和輸出信號的狀態 (0或1)之間的關系,即所謂邏輯關系,采用的數學工具是邏輯代數。 一、邏輯代數基礎 在邏輯代數中變量具有二值性,即只有兩個可能的取值“0”和“1”。 (一)基本的邏輯運算 邏輯代數的基本

基于掃描D觸發器的可逆電路測試綜合方法

格式:pdf

大小:534KB

頁數:8P

4.7

為了實現可逆邏輯電路的可測性設計,充分利用可逆邏輯電路中存在的輸出引腳,提出一種可逆邏輯電路測試綜合方法.通過定義可逆邏輯門的可觀性值和可控性值的計算方法,對可逆邏輯電路的可測性進行建模;通過插入觀察點,制定了可逆組合邏輯電路可測性實現方案;通過對現有的d觸發器進行改造并構建全新的掃描d觸發器,制定了可逆時序電路的可測性邏輯實現方案;最后分析了掃描d觸發器的工作特點,規范了測試步驟,建立一種可逆邏輯電路的測試綜合方法.實驗結果表明,與現有方法相比,文中方法插入觀察點代價平均增加不到1%,但電路的可觀性平均能得到24%的改善.

數字電路基礎D0303B數據分配器和數據選擇器

格式:pdf

大小:421KB

頁數:6P

4.6

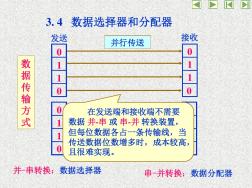

3.3.3數據分配器和數據選擇器 1.數據分配器 在數據傳輸過程中,完成將一路輸入數據分配到多路輸出端的電路稱為數據分配器。它 是一種單路輸入,多路輸出的邏輯器件,從哪一路輸出由當時的地址控制端決定。 圖3-3-13所示為四路數據分配器的邏輯電路圖。圖中d為數據輸入端,e為輸入選通 端,al、ao為地址控制輸入端,fo—f3為數據輸出端。 由圖3-3-13寫出數據分配器輸出邏輯函數的邏輯表達式: daaef010;daaef011;daeaf012;daeaf013 當e=1,alao=ll時,f3=d,其他輸出為l。其余可以類推。得到邏輯功能如表3—3—7 所示。 數據分配器也可用譯碼器來實現。 [例3-3-3]試用74ls138實現反碼輸出的8路數據分配器。 解:在圖3-3-14中,a2、al、ao用作通

數據選擇器和D觸發器的多輸入時序電路設計精華文檔

時序電路實驗仿真系統器件選擇模塊的設計

格式:pdf

大小:1.0MB

頁數:3P

4.7

時序電路實驗仿真系統包括器件選擇、連接器件和實驗測試三大模塊。文章首先對時序電路實驗仿真系統進行可行性的分析,然后介紹了用多媒體軟件flash對器件選擇模塊的應用,并對該模塊的設計做了詳細、全面的剖析,對仿真的技術、操作、實現等方面進行了深入的探討,最后提出了一些尚存在的問題及解決方向。

基于FPGA的TDI-CCD時序電路設計

格式:pdf

大小:1.5MB

頁數:4P

4.7

介紹tdi-ccd的特點、工作原理,根據項目所使用的tdi-ccd的使用要求,設計一種基于altera公司的現場可編程門陣列(fpga)ep3c25q240的tdi-ccd驅動時序電路,驅動時序使用vhdl語言編寫,在quartusⅱ平臺上進行時序仿真,通過在硬件電路中的測試結果表明,驅動時序滿足該款產品的要求。該實驗的主要目的是驗證這款tdi-ccd的性能,為其應用和進一步的性能改善獲得必要的數據,以促進國產ccd的發展及應用。

基于GAL的焊接電源時序電路設計

格式:pdf

大小:361KB

頁數:3P

4.5

文章介紹了焊機電源采用通用陣列邏輯gal(genericarraylogic)芯片進行的電路功能設計、硬件設計及gal16v8芯片的工作原理及程序設計。gal是littice公司研制的一種可電改寫、可重編程的低密度pld器件,取代了傳統的通用數字電路,提高了時序設計的靈活性。

基于R-SET結構的邏輯門電路和觸發器設計

格式:pdf

大小:491KB

頁數:未知

4.8

提出一種基于單電子晶體管的新型電路結構——r-set結構,并從r-set結構的反相器著手對該結構電路的工作原理和性能進行了分析.構造出基于r-set結構的或非門、一位數值比較器、sr鎖存器和d觸發器.通過對各電路進行spice仿真,驗證了各電路的正確性.最后對r-set和互補型set2種結構的d觸發器進行性能比較,得出r-set結構的d觸發器具有結構簡單,功耗低,延時小的特點.

數據選擇器和D觸發器的多輸入時序電路設計最新文檔

測量電路中的電路設計和儀器選擇

格式:pdf

大小:57KB

頁數:1P

4.5

電路設計具有培養和檢查學生創造性思維能力、綜合分析能力以及實驗能力等多方面能力的特點,是近幾年高考實驗考查的主要考點,它包括測量電阻值rr、電阻事ρ、電功率p和電源電動勢e及內阻r.

4位輸入數據的一般數值比較器電路設計

格式:pdf

大小:946KB

頁數:16P

4.3

課程設計報告 課程名稱數字邏輯課程設計 課題4位輸入數據的一般數值的比較 電路的設計 專業計算機科學與技術 班級計算機1202 學號201203010202 姓名周逢露 指導教師劉洞波陳淑紅陳多 2013年12月13日 課程設計任務書 課程名稱數字邏輯課程設計 課題4位輸入數據的一般數值 比較電路的設計 專業班級計算機科學與技術 學生姓名周逢露 學號201203010202 指導老師劉洞波陳淑紅陳多 審批劉洞波 任務書下達日期:2013年12月13日 任務完成日期:2014年01月21日 一、設計內容與設計要求 1.設計內容: 本課程是一門專業實踐課程,學生必修的課程。其目的和作用是使學生能將已學過的數字電 子系統設計、vhdl程序設計等知識綜合運用于電子系統的設計

一種具有掉電數據保持功能的觸發器設計

格式:pdf

大小:382KB

頁數:未知

4.7

提出了一種用相變器件作為可擦寫存儲單元的具有掉電數據保持功能的觸發器電路.該觸發器由四部分組成:具有恢復掉電時數據的雙置位端觸發器dff、上電掉電監測置位電路(poweron/offreset)、相變存儲單元的讀寫電路(readwrite)和reset/set信號產生電路,使之在掉電時能夠保存數據,并在上電時完成數據恢復.基于0.13μmsmic標準cmos工藝,采用candence軟件對觸發器進行仿真,掉電速度達到0.15μs/v的情況下,上電時可以在30ns內恢復掉電時的數據狀態.

電容快放電型觸發器的電路分析與設計

格式:pdf

大小:1.1MB

頁數:7P

4.3

為獲得快前沿的高電壓脈沖,分析了電容放電型觸發器的電路,利用簡化的等效電路研究了放電回路參數和氣體開關的火花通道電阻、電感對觸發脈沖上升時間的影響。分析了電壓波在高阻抗負載上形成觸發脈沖的過程,討論了不同置地元件對輸出波形的影響。在此基礎上,給出了快前沿的電容放電型觸發器的基本設計原則,并完成了30與100kv快前沿觸發器的設計。結果表明,30kv觸發器輸出脈沖的前沿約12ns,高阻抗負載上的幅值可達44kv;100kv觸發器輸出脈沖的前沿約10ns,高阻抗負載上的幅值可達170kv。

基于電路定量理論的五值門電路和觸發器設計

格式:pdf

大小:765KB

頁數:5P

4.7

提出六值代數,建立五值電路三要素理論(信號,網絡和負載理論),作為定量研究五值電路的數學工具。在此基礎上,首先用δ展開法由五值門函數設計了五值門電路的元件級結構。接著由d觸發器的特征方程設計了動態和靜態五值d觸發器的二種電路結構。計算機模擬驗證了上述理論和依此理論設計的電路的正確性。

基于時序電路的移位相加型8位硬件乘法器設計

格式:pdf

大小:297KB

頁數:2P

4.8

由八位加法器構成的以時序邏輯方式設計的八位乘法器,具有一定的實用價值,而且由fpga構成實驗系統后,可以很容易的用asic大型集成芯片來完成,性價比高,可操作性強。

利用觸發器進行數據實時傳輸的設計與實現

格式:pdf

大小:403KB

頁數:3P

4.7

利用sqlserver2000數據庫自身的觸發器功能,設計了一種數據實時傳輸的方式,簡化了網絡通信模塊的程序設計,提高了系統的可擴展性和可維護性。

時序電路——電子鐘的設計

格式:pdf

大小:191KB

頁數:2P

4.7

時序邏輯電路(sequentiallogiccircuit)輸出不僅取決于當前輸入信號,而且取決于電路之前所處的狀態。基本的時序電路單元有觸發器(d、jk、t等觸發器)、鎖存器、計數器等。vhdl中,時序電路通過process(clk)和ifclk’eventandclk=‘1’then邊沿檢測語句實現觸發器風格的電路;具有非完分支的if、case語句形成鎖存器電路。

數據選擇器和D觸發器的多輸入時序電路設計相關

文輯推薦

知識推薦

百科推薦

職位:暖通設計工程師

擅長專業:土建 安裝 裝飾 市政 園林