卡諾圖在時序邏輯電路設計中的應用

格式:pdf

大小:149KB

頁數:2P

人氣 :68

4.6

在數字電路的分析與設計中,經常會用到卡諾圖,因此,本文著重對時序邏輯電路設計中卡諾圖的應用進行分析。首先,介紹建立卡諾圖模型的方法,然后對卡諾圖在時序邏輯電路設計中的應用方法進行討論,最后探討卡諾圖的應用注意事項。文章對卡諾圖初學者在學習中容易出現的誤區進行總結與歸納,讓初學者注意容易出現錯誤的地方,最終實現對卡諾圖的熟練掌握與靈活應用。

FPGA在時序邏輯電路設計中的應用

格式:pdf

大小:824KB

頁數:4P

介紹了fpga器件的基本結構及設計特點,分析了采用fpga進行電路設計的優勢。選用altera公司的flex10k系列fpga器件epf10k10lc84-4,以交通信號燈控制系統為例,討論了采用fpga進行時序邏輯電路設計的思路與方法,使用硬件描述語言veriloghdl作為輸入,給出了核心部分的主要程序代碼。最后進行了時序波形的仿真,并對相關波形中出現的毛刺現象進行了相應分析。

編輯推薦下載

基于可編程計數器的時序邏輯電路設計

格式:pdf

大小:1.0MB

頁數:5P

4.6

介紹了基于msi可編程計數器74ls161的時序邏輯電路設計技術,目的是探索msi可編程計數器實現一般時序邏輯電路的擴展應用方法,即以計數器q3,q2,q1,q0端的代碼組合表示時序邏輯電路的各個狀態,由輸入變量控制計數器的ep,et及■端,綜合利用計數、置數、保持功能,使計數器的狀態變化滿足所要求的時序,用計數功能實現"次態=現態+1"的二進制時序關系,用置數功能實現"次態=預置數"的非二進制時序關系,用保持功能實現"次態=現態"的自循環時序關系。所述方法的創新點是提出了msi可編程計數器改變應用方向的邏輯修改方法。

卡諾圖在時序邏輯電路設計中應用熱門文檔

一種基于時序邏輯電路的延時開關設計

格式:pdf

大小:387KB

頁數:3P

4.3

時序邏輯電路設計是《數字電子技術》課程中一個難度大、綜合性高的部分,它綜合了組合邏輯電路和時序邏輯電路的內容。在進行狀態機設計時,隨著輸入邏輯變量的增加,狀態數目將呈指數倍急劇增加,這會使整個設計變得復雜且容易出錯。以一個延時開關控制器的設計為例,提出了一種狀態機輸入變量簡化的方法,降低了設計過程的復雜程度。

組合邏輯電路設計在EDA技術中的應用

格式:pdf

大小:203KB

頁數:1P

4.4

multisim9軟件是專門用于電子電路仿真與設計的eda軟件,本文將設計一個舉重裁判表決電路的組合電路實例應用到eda中,將理論教學與eda技術的結合在一起,為學習數字電子技術的理論知識拓展了空間。

任務驅動法在\"組合邏輯電路設計與仿真\"中的應用

格式:pdf

大小:750KB

頁數:3P

4.7

采用任務驅動法進行教學,通過任務創建、分析、問題引領進行電路設計任務,通過用multisim12.0創建測試電路并進行仿真,結合用數字實驗箱動手連線驗證,提高了學生學習興趣,培養學生的創新意識.

定時控制器邏輯電路設計

格式:pdf

大小:79KB

頁數:12P

4.6

. . 一概述 為了能使儀器在特定的時間內工作,通常需要人在場干預才能完成。本課題設計的定時器,就是能 使你不在時,儀器也能按時打開和關閉。例如你想用錄音機、錄像機錄下某一時間斷的節目,而這一段 時間你又有其他事要做,不在家或機器旁邊,你就可以實現預置一下定時器。在幾點幾分準時打開機器, 到某時某刻關掉機器。數字鐘是采用數字電路實現對時、分、秒數字顯示的計時裝置,以其顯示的 直觀性、走時準確穩定而受到人們的歡迎,廣泛用于個人家庭、車站、碼頭、辦公室等公共場所, 給人們的生活、學習、工作、娛樂帶來了極大的方便,諸如定時自動報警、按時自動打鈴、時間程 序自動控制、定時廣播、通斷動力設備、以及各種定時電氣的自動啟用等,所有這些,都是以鐘表 數字化為基礎的。 定時控制器由供電單元、數字鐘單元、定時單元以及控制輸出單元等幾部分組成.如圖1所示為定 時控制器系統框圖。 圖

卡諾圖在時序邏輯電路設計中應用精華文檔

鐵路平交道柵門控制器邏輯電路設計

格式:pdf

大小:840KB

頁數:17P

4.7

[在此處鍵入] 內蒙古工業大學本科課程設計說明書 課程設計說明書 題目:鐵路平交道柵門控制器邏輯電路設計 學生姓名: 學院: 班級: 指導教師: 二○一六年七月一日 學校代碼:10128 學號: [在此處鍵入] 內蒙古工業大學本科課程設計說明書 [在此處鍵入] 內蒙古工業大學本科課程設計說明書 摘要 鐵道平交道柵門控制器是設計一個電路來控制道柵門的放下和升起,在鐵道上放置 p1、p2兩點放置壓敏傳感器,用以感測火車是否經過,此兩點相距足夠遠,同一列 火車不能同時被此兩處壓敏傳感器,當火車任何部位位于p1、p2兩處之間時,平交 道柵門應放下,否則升起柵門。用j1、j2兩個開關模擬壓敏傳感器,輸出的信號經 電路達到設計目的,即當火車經過時,信號燈亮(或變為紅燈),柵門放下,禁止車 輛通過;當火車駛過路口時,信號燈滅(或

定時控制器邏輯電路設計(20201012164824)

格式:pdf

大小:87KB

頁數:12P

4.3

1 一概述 為了能使儀器在特定的時間內工作,通常需要人在場干預才能完成。本課題設計的定時器,就是能 使你不在時,儀器也能按時打開和關閉。例如你想用錄音機、錄像機錄下某一時間斷的節目,而這一段 時間你又有其他事要做,不在家或機器旁邊,你就可以實現預置一下定時器。在幾點幾分準時打開機器, 到某時某刻關掉機器。數字鐘是采用數字電路實現對時、分、秒數字顯示的計時裝置,以其顯示的 直觀性、走時準確穩定而受到人們的歡迎,廣泛用于個人家庭、車站、碼頭、辦公室等公共場所, 給人們的生活、學習、工作、娛樂帶來了極大的方便,諸如定時自動報警、按時自動打鈴、時間程 序自動控制、定時廣播、通斷動力設備、以及各種定時電氣的自動啟用等,所有這些,都是以鐘表 數字化為基礎的。 定時控制器由供電單元、數字鐘單元、定時單元以及控制輸出單元等幾部分組成.如圖1所示為定 時控制器系統框圖。 圖1

可編程邏輯器件在搶答器電路設計中的應用

格式:pdf

大小:661KB

頁數:5P

4.8

針對實際應用的需要,利用可編程邏輯器件設計了搶答器.該搶答器單元電路的軟件設計分別利用原理圖設計、硬件描述語言設計完成.設計了控制主電路、數字顯示電路、倒計時顯示、違犯規定電路、編碼譯碼電路功能,并利用美國altera公司的max-plusii工具軟件完成了編譯仿真驗證;硬件選擇altera的max74000s系列的epm7128lc84-15芯片來實現搶答器的系統功能.該搶答器具有很強的功能擴充性,應用效果良好.

粒計算在數字邏輯電路分析與設計中的應用

格式:pdf

大小:85KB

頁數:1P

4.6

數字邏輯電路的分析與設計需要邏輯優化的支持,通過邏輯優化可以使系統的復雜程度降低,降低系統在具體運行過程中的能耗,并且能夠使系統運行的安全性得到進一步提高。近幾年,隨著數字邏輯電路規模的不斷擴大,數字邏輯電路的分析與設計面臨著新的挑戰,因此要做好相應的分析工作。

粒計算在數字邏輯電路分析與設計中的應用

格式:pdf

大小:3.2MB

頁數:1P

4.5

數字邏輯電路的分析與設計需要邏輯優化的支持,通過邏輯優化可以使系統的復雜程度降低,降低系統在具體運行過程中的能耗,并且能夠使系統運行的安全性得到進一步提高.近幾年,隨著數字邏輯電路規模的不斷擴大,數字邏輯電路的分析與設計面臨著新的挑戰,因此要做好相應的分析工作.

卡諾圖在時序邏輯電路設計中應用最新文檔

第20章習題2-門電路和組合邏輯電路

格式:pdf

大小:693KB

頁數:38P

4.7

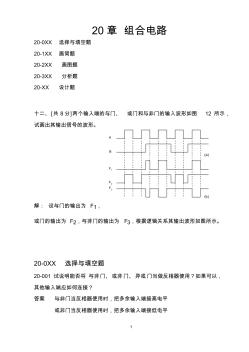

1 20章組合電路 20-0xx選擇與填空題 20-1xx畫簡題 20-2xx畫圖題 20-3xx分析題 20-xx設計題 十二、[共8分]兩個輸入端的與門、或門和與非門的輸入波形如圖12所示, 試畫出其輸出信號的波形。 解:設與門的輸出為f1, 或門的輸出為f2,與非門的輸出為f3,根據邏輯關系其輸出波形如圖所示。 20-0xx選擇與填空題 20-001試說明能否將與非門、或非門、異或門當做反相器使用?如果可以, 其他輸入端應如何連接? 答案與非門當反相器使用時,把多余輸入端接高電平 或非門當反相器使用時,把多余輸入端接低電平 a b f1 f2 f3 (a) (b) 2 異或門當反相器使用時,把多余輸入端接高電平 20-002、試比較ttl電路和cmos電路的優、缺點。 答案coms電路抗干擾能力強,速度快,靜態損耗小,工作電壓范圍

基于FPGA的TDI-CCD時序電路設計

格式:pdf

大小:1.5MB

頁數:4P

4.7

介紹tdi-ccd的特點、工作原理,根據項目所使用的tdi-ccd的使用要求,設計一種基于altera公司的現場可編程門陣列(fpga)ep3c25q240的tdi-ccd驅動時序電路,驅動時序使用vhdl語言編寫,在quartusⅱ平臺上進行時序仿真,通過在硬件電路中的測試結果表明,驅動時序滿足該款產品的要求。該實驗的主要目的是驗證這款tdi-ccd的性能,為其應用和進一步的性能改善獲得必要的數據,以促進國產ccd的發展及應用。

基于時序圖的異步時序邏輯電路的設計

格式:pdf

大小:185KB

頁數:3P

4.5

在異步時序邏輯電路的設計過程中,以波形分析為基礎,通過電路的狀態轉換圖得到電路的時序圖,通過時序圖的分析確定觸發器的時鐘方程,在時鐘方程的作用下得到狀態轉換,填寫次態卡諾圖,通過次態卡諾圖的化簡得到輸出方程和狀態方程的設計方法。該方法簡單實用,學生易于理解和接受。

基于時序圖的異步時序邏輯電路的設計??

格式:pdf

大小:185KB

頁數:3P

4.7

在異步時序邏輯電路的設計過程中,以波形分析為基礎,通過電路的狀態轉換圖得到電路的時序圖,通過時序圖的分析確定觸發器的時鐘方程,在時鐘方程的作用下得到狀態轉換,填寫次態卡諾圖,通過次態卡諾圖的化簡得到輸出方程和狀態方程的設計方法。該方法簡單實用,學生易于理解和接受。

用簡化卡諾圖設計復合氣控程序回路

格式:pdf

大小:555KB

頁數:未知

4.3

生產過程中經常需要在一臺機械上加工不同的產品或完成不同的工藝程序,此時其程序控制回路的設計與一般的程序回路設計不同,即需要把幾個單獨的順序程序合并到一個公共的回路中,采用程序選擇器使該回路按組成其回路之一的程序進行工作,這種回路稱復合氣控程序回路。用簡化卡諾圖法可以順利地解決這種復合氣控回路的設計,其關鍵是將程序選擇器h和它的輔助變量h和h看成是輔助記憶元

VHDL在數字邏輯電路設計中的應用方法

格式:pdf

大小:65KB

頁數:未知

4.6

vhdl是用于邏輯設計的硬件描述語言,具有齊全的設計技術,應用方法也比較靈活,能夠解決信息交換和設計維護方面的困難,文章介紹了vhdl語言在數字邏輯電路設計中的應用方法,以便大家更好地掌握vhdl語言的應用。

關于在液壓回路邏輯設計中用卡諾圖法簡化多變量邏輯函數的問題

格式:pdf

大小:538KB

頁數:未知

4.4

本文根據卡諾圖的對稱性,提出了簡化邏輯函數的對稱原則來代替過去所遵循的相鄰原則,從而擴大了卡諾圖法的應用范圍,使之由一般只用于四變量以下邏輯函數的簡化而能用于任何多變量邏輯函數的簡化,這就大大減少了對于復雜的液壓回路邏輯設計的困難。

卡諾圖在時序邏輯電路設計中應用相關

文輯推薦

知識推薦

百科推薦

職位:預算員主管

擅長專業:土建 安裝 裝飾 市政 園林