基于電路定量理論的五值門電路和觸發器設計

格式:pdf

大小:765KB

頁數:5P

人氣 :89

4.7

提出六值代數 ,建立五值電路三要素理論 (信號 ,網絡和負載理論 ) ,作為定量研究五值電路的數學工具。在此基礎上 ,首先用δ展開法由五值門函數設計了五值門電路的元件級結構。接著由 D觸發器的特征方程設計了動態和靜態五值 D觸發器的二種電路結構。計算機模擬驗證了上述理論和依此理論設計的電路的正確性。

門電路和觸發器

格式:pdf

大小:2.0MB

頁數:8P

1 第九節門電路和觸發器 電子電路通常分模擬電子電路和數字電子電路兩大類。前面介紹的放大電路屬于第 一類,電路中的工作信號是連續變化的電信號(模擬信號)。數字電路的基本工作信號是 二進制的數字信號,它在時間上和數值上是離散的,即不是連續漸變的,而且只有0和 1兩個基本數字,反映在電路上就是低電平和高電平兩種狀態。因此在穩態時,電路中 的半導體器件都是工作在開、關狀態。數字電路是由幾種最基本的單元電路組成的。在 這些基本單元中,對元件的精度要求不高,只要在工作時能夠可靠地區分0和1兩種狀 態就可以了。數字電路中研究的主要問題是輸入信號的狀態(0或1)和輸出信號的狀態 (0或1)之間的關系,即所謂邏輯關系,采用的數學工具是邏輯代數。 一、邏輯代數基礎 在邏輯代數中變量具有二值性,即只有兩個可能的取值“0”和“1”。 (一)基本的邏輯運算 邏輯代數的基本

編輯推薦下載

基于R-SET結構的邏輯門電路和觸發器設計

格式:pdf

大小:491KB

頁數:未知

4.8

提出一種基于單電子晶體管的新型電路結構——r-set結構,并從r-set結構的反相器著手對該結構電路的工作原理和性能進行了分析.構造出基于r-set結構的或非門、一位數值比較器、sr鎖存器和d觸發器.通過對各電路進行spice仿真,驗證了各電路的正確性.最后對r-set和互補型set2種結構的d觸發器進行性能比較,得出r-set結構的d觸發器具有結構簡單,功耗低,延時小的特點.

電路定量理論五值門電路和觸發器設計熱門文檔

電容快放電型觸發器的電路分析與設計

格式:pdf

大小:1.1MB

頁數:7P

4.3

為獲得快前沿的高電壓脈沖,分析了電容放電型觸發器的電路,利用簡化的等效電路研究了放電回路參數和氣體開關的火花通道電阻、電感對觸發脈沖上升時間的影響。分析了電壓波在高阻抗負載上形成觸發脈沖的過程,討論了不同置地元件對輸出波形的影響。在此基礎上,給出了快前沿的電容放電型觸發器的基本設計原則,并完成了30與100kv快前沿觸發器的設計。結果表明,30kv觸發器輸出脈沖的前沿約12ns,高阻抗負載上的幅值可達44kv;100kv觸發器輸出脈沖的前沿約10ns,高阻抗負載上的幅值可達170kv。

第20章習題2-門電路和組合邏輯電路

格式:pdf

大小:693KB

頁數:38P

4.7

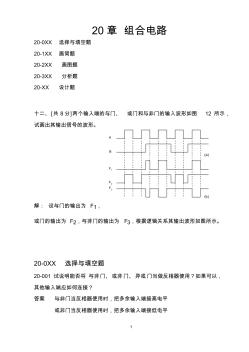

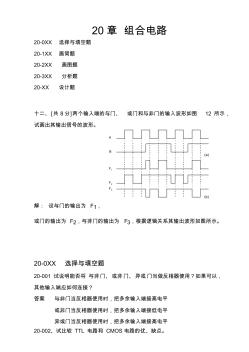

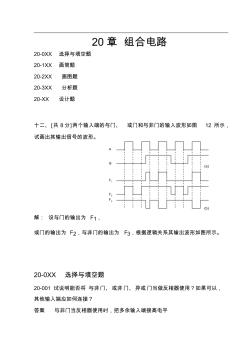

1 20章組合電路 20-0xx選擇與填空題 20-1xx畫簡題 20-2xx畫圖題 20-3xx分析題 20-xx設計題 十二、[共8分]兩個輸入端的與門、或門和與非門的輸入波形如圖12所示, 試畫出其輸出信號的波形。 解:設與門的輸出為f1, 或門的輸出為f2,與非門的輸出為f3,根據邏輯關系其輸出波形如圖所示。 20-0xx選擇與填空題 20-001試說明能否將與非門、或非門、異或門當做反相器使用?如果可以, 其他輸入端應如何連接? 答案與非門當反相器使用時,把多余輸入端接高電平 或非門當反相器使用時,把多余輸入端接低電平 a b f1 f2 f3 (a) (b) 2 異或門當反相器使用時,把多余輸入端接高電平 20-002、試比較ttl電路和cmos電路的優、缺點。 答案coms電路抗干擾能力強,速度快,靜態損耗小,工作電壓范圍

74系列門電路

格式:pdf

大小:2.3MB

頁數:23P

4.7

為了方便大家我收集了下列74系列芯片的引腳圖資料,如還有需要請上電子論壇http://ww w.dianz.cn/bbs/ 反相器驅動器ls04ls05ls06ls07ls125ls240ls244ls245 與門與非門ls00ls08ls10ls11ls20ls21ls27ls30ls38 或門或非門與或非門ls02ls32ls51ls64ls65 異或門比較器ls86 譯碼器ls138ls139 寄存器ls74ls175ls373 反相器: vcc6a6y5a5y4a4y六非門74ls04 ┌┴—┴—┴—┴—┴—┴—┴┐六非門(oc門)74ls05 _│141312111098│六非門(

電路定量理論五值門電路和觸發器設計精華文檔

基于數據選擇器和D觸發器的多輸入時序電路設計

格式:pdf

大小:680KB

頁數:3P

4.6

為了探索多輸入時序邏輯電路的簡便實現方法,介紹了基于數據選擇器和d觸發器的多輸入時序邏輯電路設計技術。即將d觸發器和數據選擇器進行組合,用觸發器的現態作為數據選擇器選擇輸入變量、數據選擇器的輸出函數作為觸發器的d輸入信號,構成既有存儲功能又有數據選擇功能的多輸入端時序網絡。由觸發器的現態選擇輸入變量、所選擇的輸入變量決定觸發器的次態轉換方向。該方法適合實現互斥多變量時序邏輯電路,且在設計過程中不需要進行函數化簡。

實現FPGA高效動態可重配置的觸發器電路

格式:pdf

大小:1.2MB

頁數:7P

4.4

設計了一種在現場可編程邏輯陣列(fpga)內可供配置的觸發器電路結構.主要特點是:不需要浪費fpga內組合邏輯的資源,就可以獨立配置出56種全部常用類型的d觸發器電路或鎖存器電路;以fpga在配置簡單時序電路時增加50%面積的代價降低了配置為復雜時序電路時70%的延時和90%的面積.同時針對xilinxvirtex系列fpga動態重配置速度較慢的缺點,在觸發器電路中加入了抓捕與寫回電路;提出了通過硬件電路來實現重配置狀態保存和寫回的方法.與xilinxvirtex器件完全用軟件實現的方法相比,加快了fpga動態重配置電路的速度.

關于數字電路中觸發器教學的幾點思考

格式:pdf

大小:92KB

頁數:1P

4.3

觸發器作為連接組合邏輯電路和時序邏輯電路這兩部分的橋梁,在整個數字電路中起著承上啟下的作用。因而,對于觸發器的掌握顯得非常重要。本文針對觸發器的教學提出了總分式,循序漸進、由淺入深,對比,抓住內在聯系,把握重點等幾條原則,希望能給大家學習觸發器帶來幫助。

觸發電路

格式:pdf

大小:205KB

頁數:5P

4.5

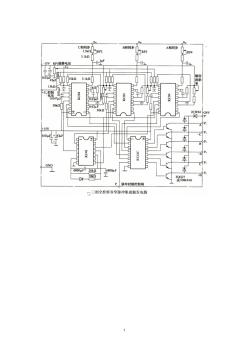

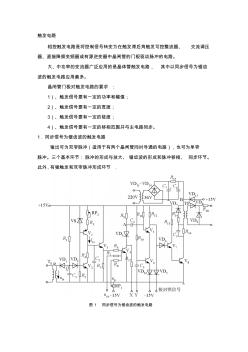

觸發電路 相控觸發電路是將控制信號轉變為在觸發滯后角觸發可控整流器、交流調壓 器、直接降頻變頻器或有源逆變器中晶閘管的門極驅動脈沖的電路。 大、中功率的變流器廣泛應用的是晶體管觸發電路,其中以同步信號為鋸齒 波的觸發電路應用最多。 晶閘管門極對觸發電路的要求: 1)、觸發信號要有一定的功率和幅值; 2)、觸發信號要有一定的寬度; 3)、觸發信號要有一定的陡度; 4)、觸發信號要有一定的移相范圍并與主電路同步。 1.同步信號為鋸齒波的觸發電路 輸出可為雙窄脈沖(適用于有兩個晶閘管同時導通的電路),也可為單窄 脈沖。三個基本環節:脈沖的形成與放大、鋸齒波的形成和脈沖移相、同步環節。 此外,有強觸發和雙窄脈沖形成環節. 圖1同步信號為鋸齒波的觸發電路 1)脈沖形成環節 v4、v5—脈沖形成 v7、v8—脈沖放大 控制電壓uco加在v4基極上 脈沖前沿由

可重復觸發單穩態觸發器在檢測電路中的應用

格式:pdf

大小:1.4MB

頁數:3P

4.8

"555"定時器是一種數模混合中的規模集成電路,它使用靈活、方便,被廣泛應用于脈沖的產生、整形、定時和延遲等電路中。由其構成的可重復觸發單穩態觸發器,能比較方便地得到持續時間更長的輸出脈沖寬度。本文介紹了由555定時器構成的可重復觸發單穩態觸發器的電路構成與工作原理,以人體心律監視電路中失落脈沖檢測為例,討論了其在信號檢測電路中的應用,說明在實際生產中,只要將其各個功能加以綜合應用,便可得到許多實用電路。

電路定量理論五值門電路和觸發器設計最新文檔

66第20章習題2-門電路和組合邏輯電路

格式:pdf

大小:601KB

頁數:27P

4.7

20章組合電路 20-0xx選擇與填空題 20-1xx畫簡題 20-2xx畫圖題 20-3xx分析題 20-xx設計題 十二、[共8分]兩個輸入端的與門、或門和與非門的輸入波形如圖12所示, 試畫出其輸出信號的波形。 解:設與門的輸出為f1, 或門的輸出為f2,與非門的輸出為f3,根據邏輯關系其輸出波形如圖所示。 20-0xx選擇與填空題 20-001試說明能否將與非門、或非門、異或門當做反相器使用?如果可以, 其他輸入端應如何連接? 答案與非門當反相器使用時,把多余輸入端接高電平 或非門當反相器使用時,把多余輸入端接低電平 異或門當反相器使用時,把多余輸入端接高電平 20-002、試比較ttl電路和cmos電路的優、缺點。 a b f1 f2 f3 (a) (b) 答案coms電路抗干擾能力強,速度快,靜態損耗小,工作電壓范圍寬, 有取代

第20章習題2-門電路和組合邏輯電路 (2)

格式:pdf

大小:711KB

頁數:44P

4.3

20章組合電路 20-0xx選擇與填空題 20-1xx畫簡題 20-2xx畫圖題 20-3xx分析題 20-xx設計題 十二、[共8分]兩個輸入端的與門、或門和與非門的輸入波形如圖12所示, 試畫出其輸出信號的波形。 解:設與門的輸出為f1, 或門的輸出為f2,與非門的輸出為f3,根據邏輯關系其輸出波形如圖所示。 20-0xx選擇與填空題 20-001試說明能否將與非門、或非門、異或門當做反相器使用?如果可以, 其他輸入端應如何連接? 答案與非門當反相器使用時,把多余輸入端接高電平 a b f1 f2 f3 (a) (b) 或非門當反相器使用時,把多余輸入端接低電平 異或門當反相器使用時,把多余輸入端接高電平 20-002、試比較ttl電路和cmos電路的優、缺點。 答案coms電路抗干擾能力強,速度快,靜態損耗小,工作電壓范圍寬, 有取代

一種基于D觸發器的調制編碼板故障記憶電路設計

格式:pdf

大小:154KB

頁數:2P

4.7

對于廣播發射機的日常維護工作,準確的判斷發射機的故障點是快速處理發射機故障的先決條件。在dx-200型中波發射機中,一些故障由于故障指示瞬間消失或者故障指示不能覆蓋到給維護人員判斷故障位置、縮短處理故障的時間帶來了負擔。以調制編碼板的電源故障指示電路為載體,本文用d觸發器設計出一種穩定可靠的故障點記憶電路,在實際運行中把故障現場保持記憶,留給維護人員,大大提高了故障處理效率。

基于Multisim與邏輯門電路的交通燈檢測電路設計

格式:pdf

大小:110KB

頁數:未知

4.6

multisim是一款穩定性強,操作簡單的電子設計軟件。本文利用該軟件,與若干門電路,來設計一個檢測交通燈是否正常工作的簡易檢測電路。通過實驗仿真,說明利用multisim軟件可以設計出這種檢測電路。

測量電路中的電路設計和儀器選擇

格式:pdf

大小:57KB

頁數:1P

4.5

電路設計具有培養和檢查學生創造性思維能力、綜合分析能力以及實驗能力等多方面能力的特點,是近幾年高考實驗考查的主要考點,它包括測量電阻值rr、電阻事ρ、電功率p和電源電動勢e及內阻r.

邏輯門電路使用中的幾個實際問題

格式:pdf

大小:176KB

頁數:9P

4.5

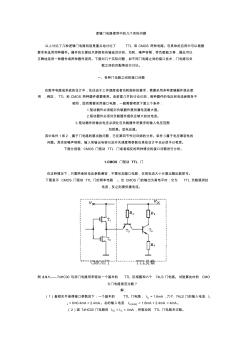

邏輯門電路使用中的幾個實際問題 以上討論了幾種邏輯門電路特別是重點地討論了ttl和cmos兩種電路。在具體的應用中可以根據 要求來選用何種器件。器件的主要技術參數有傳輸延遲時間、功耗、噪聲容限,帶負載能力等,據此可以 正確地選用一種器件或兩種器件混用。下面對幾個實際問題,如不同門電路之間的接口技術,門電路與負 載之間的匹配等進行討論。 一、各種門電路之間的接口問題 在數字電路或系統的設計中,往往由于工作速度或者功耗指標的要求,需要采用多種邏輯器件混合使 用,例如,ttl和cmos兩種器件都要使用。由前面幾節的討論已知,每種器件的電壓和電流參數各不 相同,因而需要采用接口電路,一般需要考慮下面三個條件: 1.驅動器件必須能對負載器件提供灌電流最大值。 2.驅動器件必須對負載器件提供足夠大的拉電流。 3.驅動器件的輸出電壓必須處在負載器件所要求的輸入電壓范圍 ,包括高。低電壓

電路定量理論五值門電路和觸發器設計相關

文輯推薦

知識推薦

百科推薦

職位:中/高級建筑師

擅長專業:土建 安裝 裝飾 市政 園林