格式:pdf

大小:744KB

頁數: 4頁

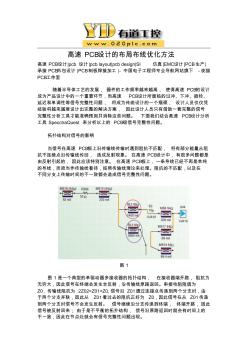

高速 PCB設計的布局布線優化方法 高速 PCB設計 |pcb 設計 |pcb layout|pcb design|SI 仿真 |EMC設計 |PCB生產 | 承接 PCB外包設計 |PCB制板焊接加工 |- 中國電子工程師專業導航網站旗下 -夜貓 PCB工作室 隨著半導體工藝的發展, 器件的工作頻率越來越高, 使得高速 PCB的設計 成為產品設計中的一個重要環節,而高速 PCB設計所面臨的過沖、下沖、振鈴、 延遲和單調性等信號完整性問題, 將成為傳統設計的一個瓶頸, 設計人員僅僅憑 經驗將越來越難設計出完整的解決方案, 因此設計人員只有借助一套完整的信號 完整性分析工具才能準確預測并消除這些問題。 下面我們結合高速 PCB設計分析 工具 SpecctraQuest 來分析以上的 PCB級信號完整性問題。 拓撲結構對信號的影響 當信號在高速 PCB板上沿傳輸線傳輸時遇到阻抗不匹配, 將有部

格式:pdf

大小:263KB

頁數: 8頁

信號完整性技術分析 學院:電氣學院 姓名:趙家謂 學號: 3090504051 專業:電子信息科學與技術 摘要 隨著微電子技術和計算機技術的不斷發展, 信號完整性分析的應用已經成為 解決高速系統設計的唯一有效途徑。 借助功能強大的 Cadence公司 SpecctraQuest 仿真軟件,利用 IBIS 模型,對高速信號線進行布局布線前信號完整性仿真分析 是一種簡單可行行的分析方法, 可以發現信號完整性問題, 根據仿真結果在信號 完整性相關問題上做出優化的設計,從而縮短設計周期。 本文概要地介紹了信號完整性 (SI)的相關問題,基于信號完整性分析的 PCB設計 方法,傳輸線基本理論, 詳盡的闡述了影響信號完整性的兩大重要因素 —反射和 串擾的相關理論并提出了減小反射和串擾得有效辦法。 討論了基于 SpecctraQucst 的仿真模型的建立并對仿真結果進行了分析。 研究結果表明在高速電路

熱門知識

高速pcb設計-

話題: 地產家居duanwei100

精華知識

高速pcb設計最新知識

高速pcb設計-

話題: 工程造價panjun1968

相關問答

高速pcb設計-

話題: 路橋市政diyutiansh0

-

話題: 路橋市政Steven2006

-

話題: 工程造價xunbozhang

- 資潼高速公路路線圖

- 長臨高速圖紙線路有變動嗎

- 湖南省高速公路地圖

- 高德地圖怎么沒有京臺高速

- 高速公路斷面工程圖

- 二廣高速公路路線圖

- 日東高速公路路線圖

- 如何熟悉湖北省高速地圖

- g22高速公路243km地圖

- 高速鐵路設計規范2019

- 分形DGS單元結構設計及其在微帶電路中的應用

- 逆變TIG焊機接觸引弧電路的設計(引弧電路)

- 以MSP430FW427為核心的遠程數字水表設計

- 億陽信通中標環城高速公路晉江至石獅段機電工程項目

- 中國水電路橋武邵高速公路六標項目質量檢驗試驗計劃

- 引江濟淮工程淠河總干渠以北安徽段截污導流工程設計

- 中華大廈五層宏遠公司辦公室內裝修工程施工組織設計

- 基于超磁致伸縮效應的新型液壓高速開關閥

- 招遠電視臺制作播出系統數字化改造工程的設計與實踐

- 全熱回收地源熱泵空調機組的系統及工程方案設計

- 展覽館裝飾工程消防改造施工組織設計方案(91頁)

- 乍嘉蘇高速公路改性瀝青SMA—13面層試驗段施工

- 支持群體設計的工程數據庫管理系統的結構及實現

- 智能建筑工程設計中的機電設備集成配置系統總體設計

- 中國石化北京設計院標準工藝裝置管道墊片選用規定

- 中航格瀾陽光花園一期門禁對講建設項目施工組織設計

- 在書香中沉睡——“川大河畔”高尚住宅小區景觀設計

- 消防機房的設計規范

- 七氟丙烷主要設計參數

- 車輛道閘系統設計方案

- 機械設計服務

- 機器視覺系統設計

- 消防圖標設計方案

- tt接地系統設計規范

- 火災報警設計新規范

- 噪聲監測報警系統設計

- 汽車防撞報警器的設計

- 模擬醫院報警系統設計

- 單片機溫控報警設計

- 凈水系統設計方案

- 智能車庫系統設計原理

- 智能車庫畢業設計

- 超濾系統設計計算

- 公園景遮陽景觀傘設計

- 農村2層小洋樓設計圖

- 120平米套房平面設計圖

- 變剛度調平設計

- 路基壓密注漿加固設計

- 幼兒園教室門設計圖片

- 高壓柜設計接地刀

- 荷載設計值和標準值

- so2填料吸收塔的設計

- 地下車庫人防怎么設計

- 常用機械設計公式及應用實例

- 展覽與展示設計

- 村莊建設規劃設計

- 家庭小院子設計圖